# **Digital to Analog Converter**

# Analog to Digital Converter

**DAC - ADC**

EIM Chap 2 – Digital to analog converter . Analog to digital converter

## **Digital to Analog Converter**

- Function: converts binary input number in analog output;  $f_{DAC}:N \rightarrow \mathbf{R}$

- Parameters:

- Conversion type: unipolar, bipolar;

- Binary code (offset binary, two's complement, etc.);

- Output type (U, I);

- Output range  $\Delta U = U_{O_{max}} U_{O_{min}}$   $\Delta I = I_{O_{max}} I_{O_{min}}$

- Resolution output variation for LSB variation of input code

$$\delta U = U_{LSB} = \Delta U / (2^n - 1)$$

- number of bits used for binary cod (n)

Settling time - interval between an input command and the time when the output reaches its final value;

- Binary representation (positive fixed point) of numbers (n<sub>1</sub>+n<sub>2</sub>+1 bits):  $N = \sum_{k=1}^{n_2} b_k 2^k$ ;  $b_k \in \{0,1\}$ ;

- **Binary coding** (sub-unitary, N < 1)<sup>k=-n1</sup>

- Natural binary (unsigned)

$$N = \sum_{k=1}^{n} b_k 2^{-k} \qquad N_{\min} = 0 \qquad N_{\max} = 1 - 2^{-n} \qquad \delta N = 2^{-n}$$

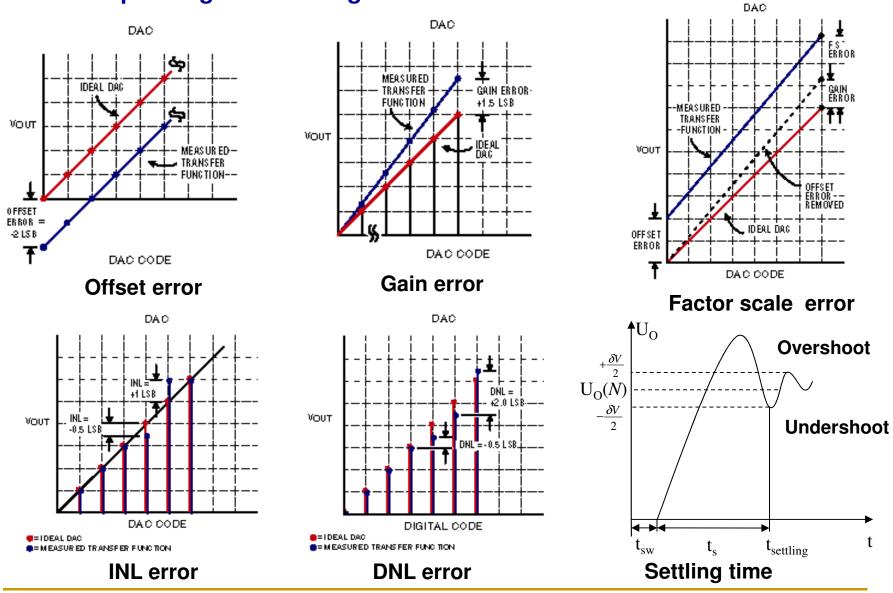

Offset binary (signed)

$$N = \sum_{k=1}^{n} b_k 2^{-k} - 2^{-1} \qquad N_{\min} = -\frac{1}{2} \qquad N_{\max} = \frac{1}{2} - 2^{-n} \qquad \delta N = 2^{-n}$$

Two's complement (signed)

$$N = (-2^{-1}) \cdot b_1 + \sum_{k=2}^n b_k 2^{-k} \qquad N_{\min} = -\frac{1}{2} \qquad N_{\max} = \frac{1}{2} - 2^{-n} \qquad \delta N = 2^{-n}$$

- Binary coding (cont'd)

- Sign Magnitude (signed)

$$N = (-1)^{b_1} \cdot \sum_{k=2}^{n} b_k 2^{-k} \quad N_{\min} = -2^{-1} + 2^{-n} \quad N_{\max} = 2^{+1} - 2^{-n} \quad \delta N = 2^{-n}$$

- Binary coded decimal (BCD) 4 bits (nibble) used to represent one digit ;

- Gray the difference between codes of two successive number is 1 bit;

- One's complement (signed);

| N (natural) | Fraction ( subunitar nr) | NB   | BCD  | Gray               |

|-------------|--------------------------|------|------|--------------------|

| 0           | 0                        | 0000 | 0000 | 0000               |

| 1           | 1/16                     | 0001 | 0001 | 0001               |

| 2           | 2/16                     | 0010 | 0010 | 0011               |

| 3           | 3/16                     | 0011 | 0011 | 0010               |

| 4           | 4/16                     | 0100 | 0100 | 0110               |

| 5           | 5/16                     | 0101 | 0101 | 0111               |

| 6           | 6/16                     | 0110 | 0110 | 0101               |

| 7           | 7/16                     | 0111 | 0111 | 0100               |

| 8           | 8/16                     | 1000 | 1000 | 1100               |

| 9           | 9/16                     | 1001 | 1001 | 11 <mark>01</mark> |

| 10          | 10/16                    | 1010 | -    | 1111               |

| 11          | 11/16                    | 1011 | -    | 1110               |

| 12          | 12/16                    | 1100 | -    | 1010               |

| 13          | 13/16                    | 1101 | -    | 1011               |

| 14          | 14/16                    | 1110 | -    | 1001               |

| 15          | 15/16                    | 1111 | -    | 1000               |

#### EIM Chap 2– Digital to analog converter Unipolar Codes

#### **Bipolar Codes**

| Ν  | Fraction | SM                | C1  | C2  | OB*               | ОВ  |

|----|----------|-------------------|-----|-----|-------------------|-----|

| +3 | +3/8     | <mark>0</mark> 11 | 011 | 011 | 111               | 000 |

| +2 | +2/8     | <mark>0</mark> 10 | 010 | 010 | <mark>1</mark> 10 | 001 |

| +1 | +1/8     | <mark>0</mark> 01 | 001 | 001 | <mark>1</mark> 01 | 010 |

| +0 | +0       | 000               | 000 | 000 | 100               | 011 |

| -0 | -0       | 100               | 111 | -   | -                 | -   |

| -1 | -1/8     | 101               | 101 | 111 | <mark>0</mark> 11 | 100 |

| -2 | -2/8     | <b>1</b> 10       | 101 | 110 | <mark>0</mark> 10 | 101 |

| -3 | -3/8     | 111               | 100 | 101 | 001               | 110 |

| -4 | -4/8     | -                 | -   | 100 | 000               | 111 |

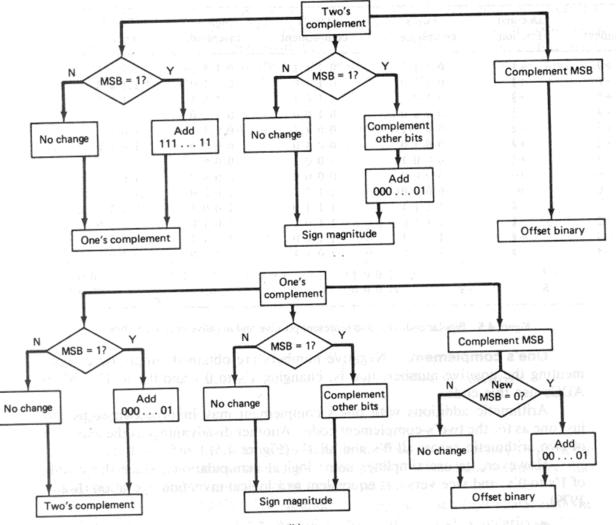

#### **Binary codes conversion**

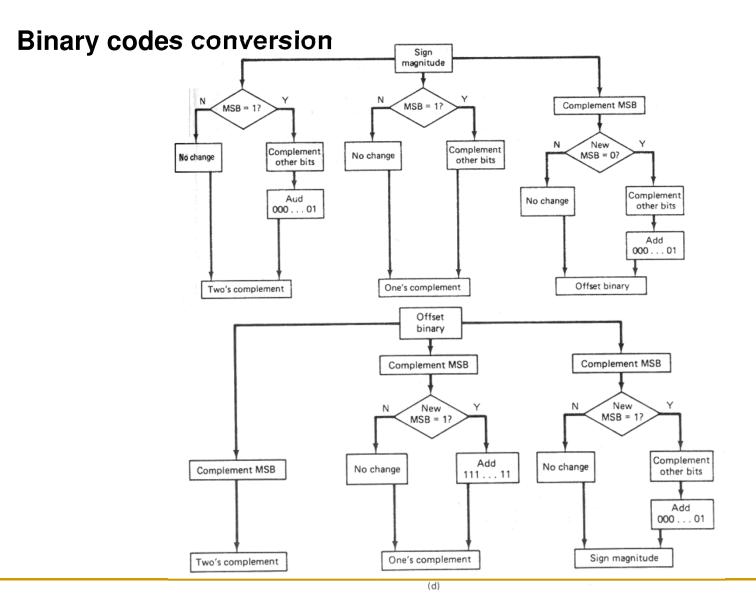

Ideal characteristic for unipolar DAC :

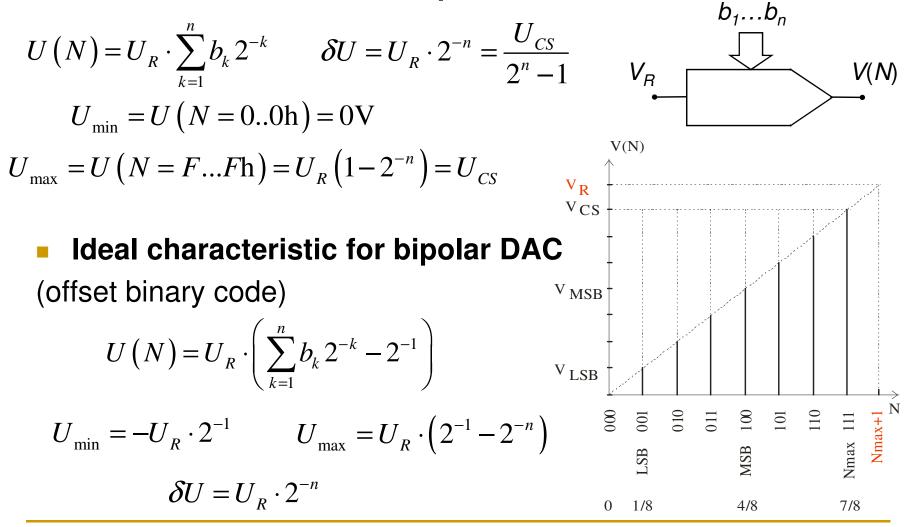

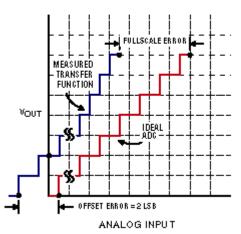

## Non-ideality errors

## Static errors

- Offset error analog output response to an input code corresponding to output zero;

- Gain error difference between slope of actual and ideal transfer function;

- Full-Scale error difference between the actual and the ideal output maximum value (offset error + gain error);

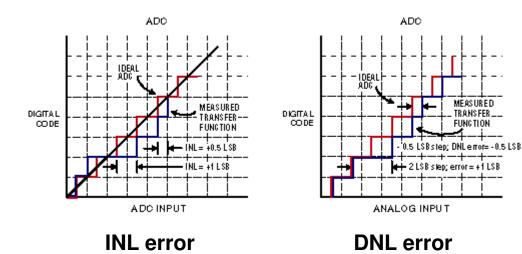

- Integrated nonlinearity error (INL) deviation of an actual transfer function from a straight line (after nullifying offset and gain errors);

- Differential nonlinearity error (DNL) difference between the ideal and the measured output responses for successive DAC codes;

- **Dynamic error**: overshoot, undershoot (during settling time)

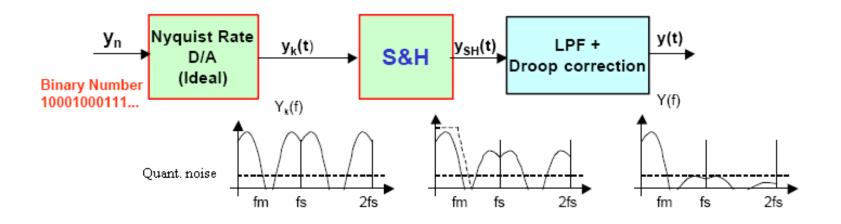

## D/A converter – traditional data converter at Nyquist rate (f<sub>s</sub>>2f<sub>m</sub>)

- LPF is antialiasing filter (for extinction of image signal on  $f_S$ );

- Droop correction means inverse "Sinc" function ;

- The S/H is a "deglitching" circuit and could be eliminated for small glitches;

#### EIM Course 3 – Digital to analog converter

## **D/A converter** – mathematical representation:

**Pulse Amplitude Modulation**

$$y_{sh}(t) = \left\{ \sum_{n=-\infty}^{+\infty} y(t) \cdot \delta(t-nT_s) \right\} \otimes p(t)$$

$$y(t) \longrightarrow p(t)$$

hold

$$\int p(t) + y_{sh}(t)$$

$$F\left\{y_{sh}(t)\right\} = F\left\{ \sum_{n=-\infty}^{+\infty} y(nT_s) \cdot \delta(t-nT_s) \right\} \cdot F\left\{p(t)\right\}$$

$$Y_{sh}(f) = w \cdot \operatorname{sinc}(\pi f \cdot w) \cdot f_s \sum_{n=-\infty}^{\infty} Y_k(f-nf_s)$$

For  $w = T_s$  (practical DAC converter)

$$f_m = \int f_m + \int$$

# Types of DAC's

- Binary Weighted Resistor Network

- R-2R Ladder Network

- Stochastic

- Multiplying DAC

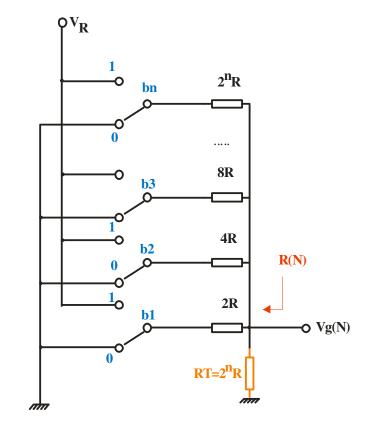

## **Binary-Weighted Resistor DAC**

Using Tellegen's theorem:

$$V_{g}(N) \cdot \left( \sum_{i=1}^{n} \frac{1}{2^{i}R} + \frac{1}{2^{n}R} \right) = V_{R} \sum_{i=1}^{n} \frac{b_{i}}{2^{i}R} \quad b_{i} \in \{0,1\}$$

$V_{g}(N) = V_{R} \sum_{i=1}^{n} b_{i} 2^{-i} = V_{R} \cdot N$

$V_{g\_\min} = V_{g}(0...0h) = 0V \quad \delta V_{g} = V_{g}(0...1h) = 2^{-n} V_{R}$

$V_{g\_\max} = V_{g}(F...Fh) = V_{R}(1-2^{-n})$

After source passivization:

$$\frac{1}{R(N)} = \sum_{i=1}^{n} \frac{1}{2^{i}R} + \frac{1}{2^{n}R} = \frac{1}{R} \implies R(N) = R$$

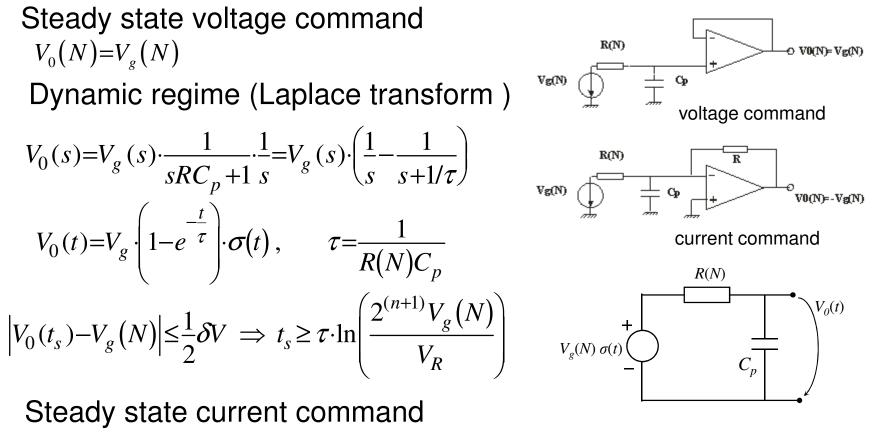

## Binary-Weighted Resistor DAC (cont'd)

$$V_0(N) = -\frac{R}{R(N)} \cdot V_g(N) = -V_g(N)$$

## Binary-Weighted Resistor DAC (cont'd)

**Disadvantages:**

- Resistance Values Require Great Accuracy:

e.g. Tolerance of R must be < 1/2<sup>n</sup>

- Often limited to 4-Bit conversions because of the limited current range possible with resistors;

- Larger bit numbers difficult due desired current changes being close in magnitude to noise amplitudes (for less significant bits);

- Hardware difficult realization for large bits number (due the weight inaccuracy for the large range);

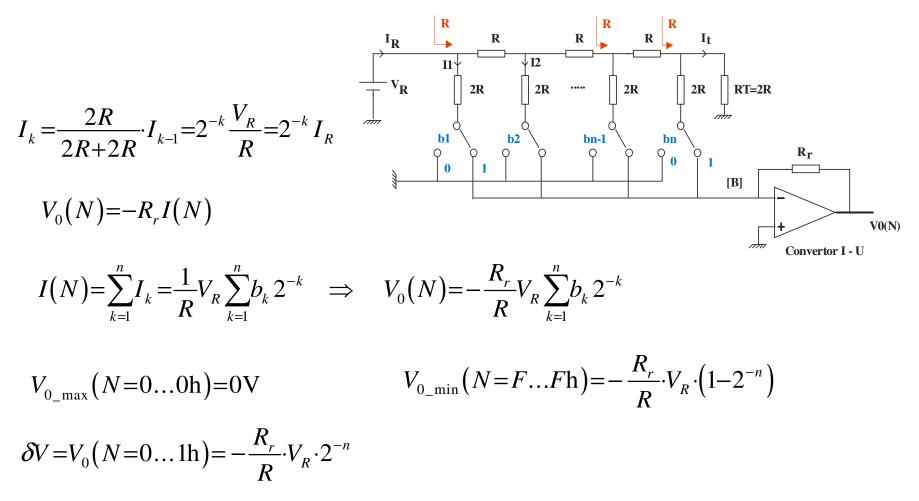

## **R-2R ladder network DAC**

## R-2R ladder network resistor DAC (cont'd)

- Maintains constant current through all branches = no voltage transients;

- Less hardware constrain (easy to find R-2R resistor pair values);

- Faster response time due to lack of voltage transients.

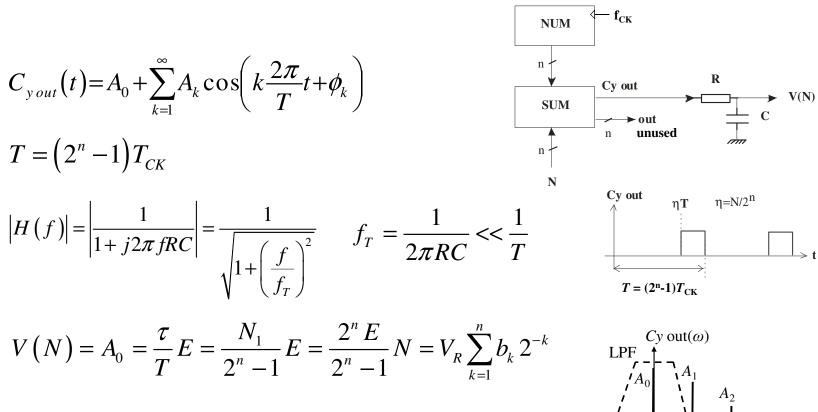

## Stochastic DAC (without resistor network)

ω

N sub-unitary number ( $N_1$  supra-unitary)

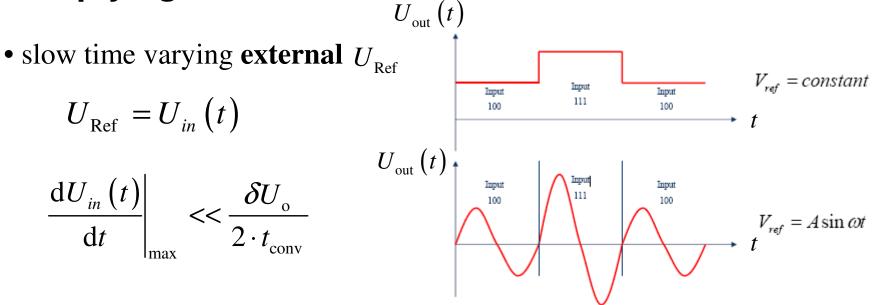

# **Multiplying DAC**

• binary code on digital input  $\rightarrow$  command for controlled amplification / attenuation;

•  $U_{in}(t)$  must preserve DAC functionality;

## **DAC** applications

- Industrial Control Systems

e.g. motor speed & valves;

- Digital Audio e.g. CD player;

- Digital Communications e.g. digital telephone and video systems;

- Waveform Function Generators e.g. direct digital synthesizer (DDS);

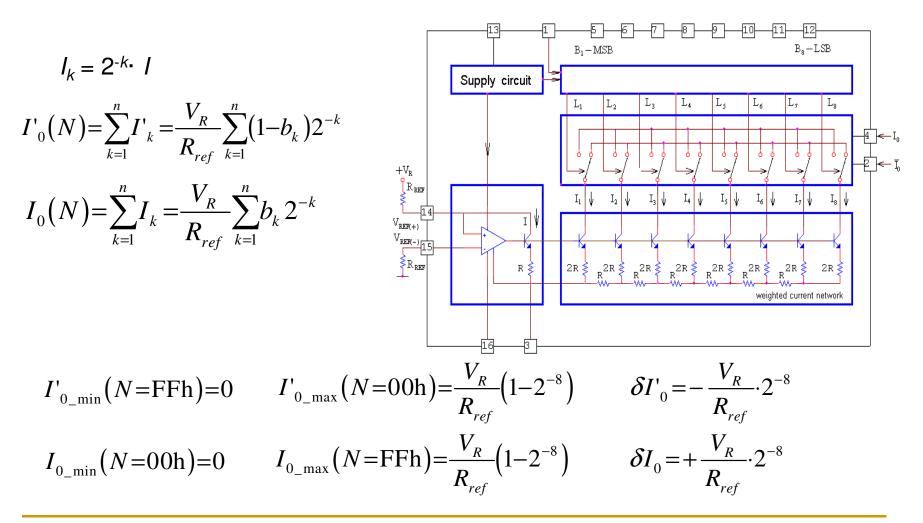

Example 1: Digital to analog converter (8 bits) - DAC 08

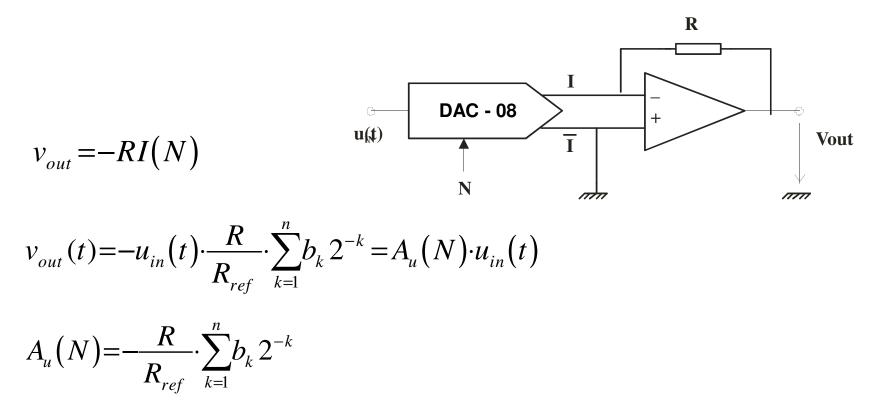

Example 2: Inversion amplifier with digital adjustment gain

## **Analog to Digital Converter**

- Function: converts input analog signal into a digital signal;

- ADC conversion comprises :

- Time sampling: samples are taken from the analog signal (sampling frequency) and its values are maintained for a certain time interval;

- Quantization : rounding off of the sampled value to the nearest of a limited number of digital values;

- Binary coding: conversion of the quantized value into a binary code;

Sampling and quantization operation may lead to loss of information.

Under certain conditions ADC loss can be limited to an acceptable minimum;

# **Analog to Digital Converter**

Mathematical representation of ADC function:

$f_{ADC}$ :  $\mathbf{R} \rightarrow \mathbf{N}$

## Parameters:

- Conversion type: unipolar, bipolar;

- Quantization type: truncate, round, round-ceiling;

- Binary code (natural, offset, two's complement, etc.);

- Input type (U, I);

- Input range;

- Resolution the smallest change required in the ADC analog input to surely change its output code by one level;

- number of bits used for binary cod (n);

- Conversion time required time before the converter can provide valid output data

- Accuracy of conversion the difference between the actual input voltage and the full-scale weighted equivalent of the binary output code

### Parameters (cont'd)

Converter Throughput Rate - the number of times the input signal can be sampled maintaining full accuracy

- Inverse of the total time required for one

successful conversion

- Inverse of conversion time if no S/H

(Sample and Hold) circuit is used;

- ADC Interface Signals :

- Data: Digital I/O pins the ADC uses to supply data

- Parallel output n+1 pins (fast transmission, short distances)

- Serial output 2 pins (for long distances, need a internal shift-register)

- Start: Pulse high to start conversion (input)

- EOC (End of Conversion): Typically active low → low level of pulse indicate complete conversion (output value can be read);

- Clock: Clock used for conversion (for synchronising ADC sub-blocks, for internal FSM);

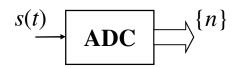

# A/D Converter – traditional data converter at Nyquist rate $(f_s > 2f_m)$

Successive operations for AD conversion process.

ADC introduces a non-compensable quantization noise.

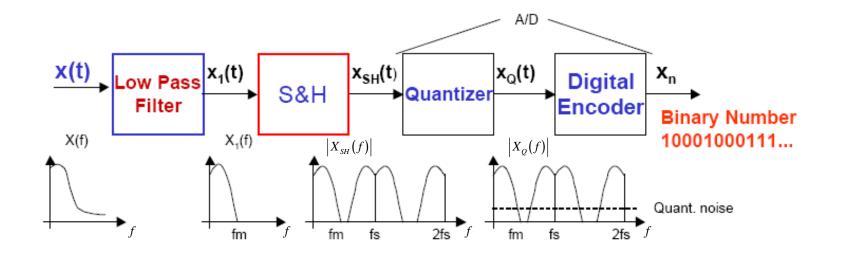

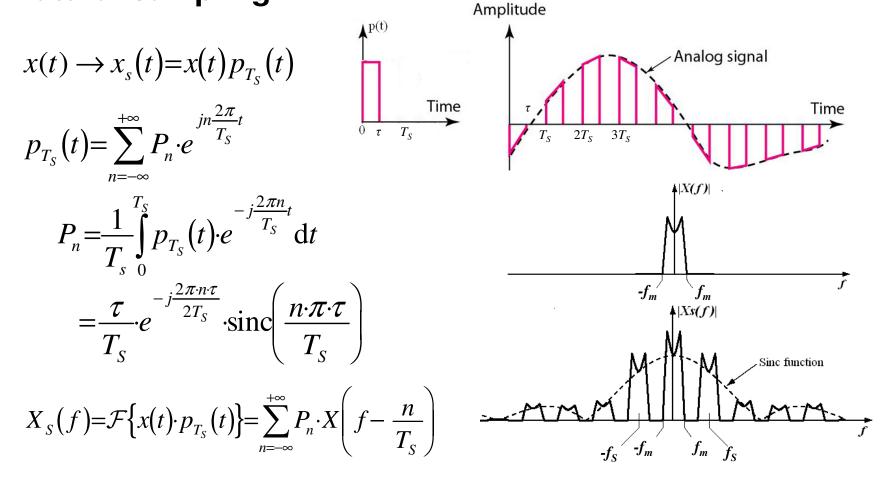

## Sampling process (remember)

- continuous signal conversion into a discrete time samplers sequence (ideal sampling, natural sampling, flat-top sampling);

# Sampling process (cont'd) •Natural sampling

30

# Sampling process (cont'd)

Flat-top sampling Amplitude Analog signal  $x(t) \to x_s(t) = \left\{ x(t) \sum_{n=-\infty}^{+\infty} \delta(t - nT_s) \right\} \otimes p(t)$ Time Time  $P(f) = \mathcal{F}\{p(t)\} = T_s \cdot e^{-j\pi f T_s} \cdot \operatorname{sinc}(\pi f T_s)$ |X(f)| $X_{s}(f) = e^{-j\pi fT_{s}} \cdot \operatorname{sinc}(\pi fT_{s}) \cdot \sum_{n=-\infty}^{+\infty} X\left(f - \frac{n}{T_{s}}\right)$ f  $f_m$  $-f_m$ Xs(f)Sinc function Sampling rate is given in Samples/s (S/s, kS/s, MS/s, GS/s);  $f_m$  $f_m$  $-f_{s}$  $f_{s}$

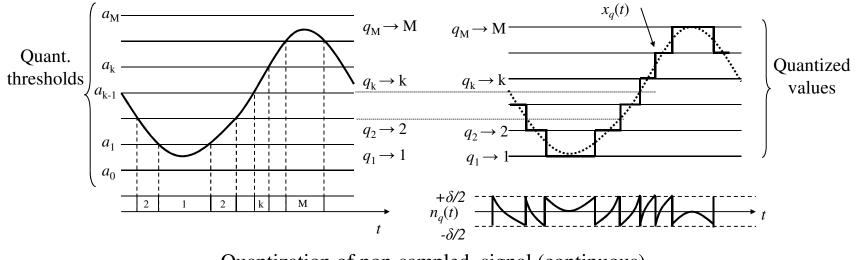

## **Quantizing process**

- analog signal approximation to the nearest discrete value:

$$x[n] \rightarrow x_q[n] = q_k \Longrightarrow k, \quad k \in 1, M, \quad q_k \in Q_M$$

Quantization of non-sampled signal (continuous)

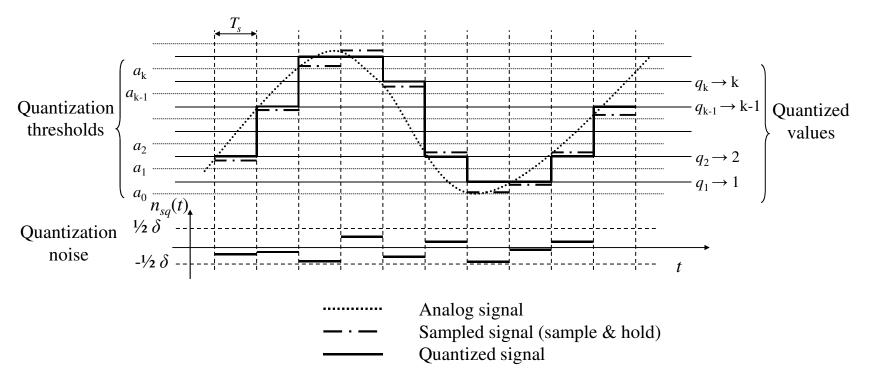

## Sampling & quantizing process

• Quantization – uniform (constant step) – linear ADC

– non-uniform (variable step) – nonlinear ADC

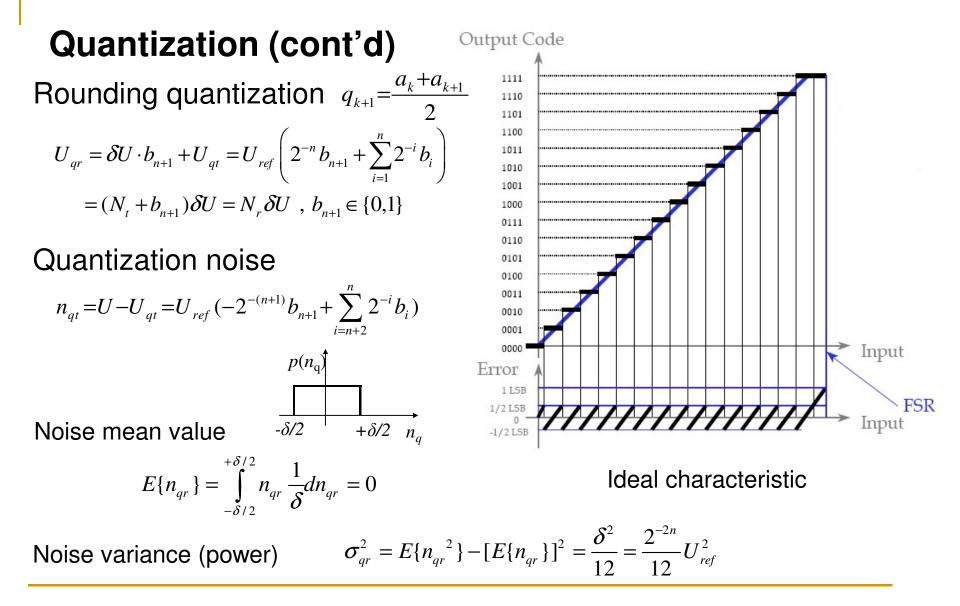

## Quantization

Truncating quantization  $q_k = a_{k-1}$ Output Code  $U_{qt} = U_{ref} \sum_{i=1}^{n} 2^{-i} b_i = \delta U \sum_{i=1}^{n} 2^{n-i} b_i = N_t \delta U$ 1111 1110 1101 1100 1011 Quantization noise  $\uparrow p(n_q)$ 1010 1001  $n_{qt} = U - U_{qt} = U_{ref} \sum_{i=n+1}^{\infty} 2^{-i} b_i$ 1000 0111 0110 0101 Noise mean value 0100 0011  $E\{n_{qt}\} = \int_{-\infty}^{\infty} p(n_{qt})n_{qt}dn_{qt} = \int_{-\infty}^{\delta} n_{qt}\frac{1}{\delta}dn_{qt} = \frac{\delta}{2}$ 0010 0001 0000 Input Error Noise variance (power) 1LSB Input  $\sigma_{qt}^{2} = E\{n_{qt}^{2}\} - [E\{n_{qt}\}]^{2} = \frac{\delta^{2}}{12} = \frac{2^{-2n}}{12}U_{ref}^{2}$ Ideal characteristic

## Quantization (cont'd)

Round-ceiling quantization  $q_k = a_k$ Output Code  $U_{qm} = \delta U + U_{qt} = U_{ref} \left( 2^{-n} + \sum_{i=1}^{n} 2^{-i} b_i \right)$ 1111 1110  $=(N_{t}+1)\delta U=N_{m}\delta U$ 1101 1100 Quantization noise 1011 1010 1001  $n_{qm} = U - U_{qm} = U_{ref} (-2^{-n} + \sum^{\sim} 2^{-i} b_i)$ 1000 0111 0110 0101 Noise mean value  $p(n_{\rm o})$ 0100 0011  $E\{n_{qm}\} = \int_{-\delta}^{0} n_{qm} \frac{1}{\delta} dn_{qm} = -\frac{\delta}{2} \qquad \frac{1}{-\delta}$ 0010 Input 0001 0000 Error Input Noise variance (power) 0 -1LSB  $\sigma_{qm}^{2} = E\{n_{qm}^{2}\} - [E\{n_{qm}\}]^{2} = \frac{\delta^{2}}{12} = \frac{2^{-2n}}{12}U_{ref}^{2}$ Ideal characteristic

### Quantization (cont'd)

Noise value as: voltage (rms, p-p), LSB (rms, p-p), SNR;

Signal to quantization noise ratio (SNR)

Considering a periodic signal at input, with period *T*, having power:

$$P_{x} = \frac{1}{T} \int_{0}^{T} x^{2} (t) dt = U_{x_{-}ef}^{2}$$

$$SNR (n) = 10 \cdot \log\left(\frac{P_{x}}{P_{n_{q}}}\right) = 10 \cdot \log\left(\frac{U_{x_{-}ef}^{2}}{\sigma_{q}^{2}}\right) = 10 \cdot \log\left(\frac{12 \cdot U_{x_{-}ef}^{2}}{\delta^{2}}\right) = 10 \cdot \log\left(2^{2n} \cdot \frac{12 \cdot U_{x_{-}ef}^{2}}{U_{ref}^{2}}\right)$$

$$= 6,02 \cdot n + 10,8 + 20 \cdot \log\left(\frac{U_{x_{-}ef}}{U_{ref}}\right) \quad [dB]$$

#### **Total SNR after quantization process:**

For analog noisy signal, the total noise power is  $\sigma_T^2 = \sigma_a^2 + \sigma_q^2$

effective bit number :

$$n_{ef} = \log_4 \frac{U_{x_-ef}^2}{\sigma_T^2} = n - \log_4 \left(1 + \frac{\sigma_a^2}{\sigma_q^2}\right)$$

### **Quantization (cont'd)**

Example: a full range sine wave input  $x(t) = A \sin(\omega t)$   $A \cong \frac{U_{ref}}{2}$ Signal power and rms value:  $P_x = \frac{1}{T} \int_{-\infty}^{T} x^2(t) dt = \frac{A^2}{2} = U_{x_-ef}^2 = \frac{U_{ref}^2}{8}$  $SNR_q(n) = 10 \cdot \log\left(\frac{P_x}{P_n}\right) = 10 \cdot \log\left(\frac{A^2}{2\sigma_q^2}\right) = 10 \cdot \log\left(\frac{6A^2}{\delta^2}\right) = 10 \cdot \log\left(\frac{3 \cdot U_{ref}^2}{2 \cdot 2^{-2n} U_{ref}^2}\right)$  $SNR_a(n) = 6.02 \cdot n + 1.76 \text{ dB}$  (for sinwave full range quantization) Dynamic range:  $DR = 20 \cdot \lg \frac{x_{\text{max}}}{2} = 20(n-1) \cdot \lg 2 \cong 6,02 \cdot n - 6.02$  $X_{\min}$  $ENOB = \left(SNR_{q} \Big|_{HP} - 1,76\right) / 6.02$  bits number for specified  $SNR_{q}$  $SNR_a$  (10 bit) = 62 dB Example:  $n_{ef} = \log_4 \frac{A^2}{\sigma_{\pi}^2} + \log_4 \frac{1}{3} = n - \log_4 \left( 1 + \frac{\sigma_a^2}{\sigma_{\pi}^2} \right)$ total effective bit number:

# Non-ideality errors

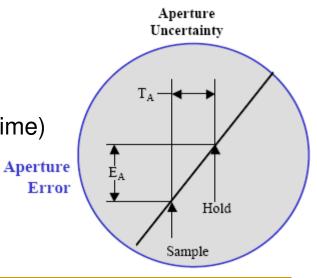

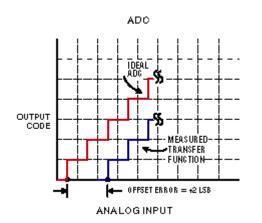

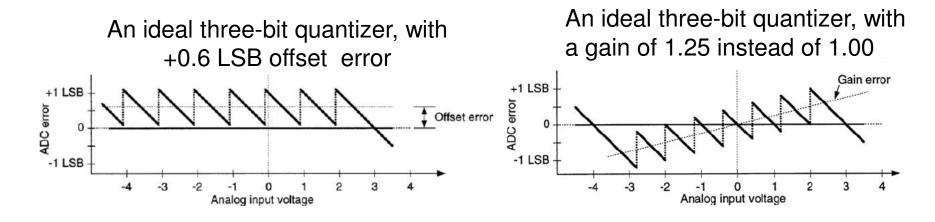

### Static errors

- Offset error (linear error);

- Gain error (linear error);

- Full-Scale error (offset error + gain error);

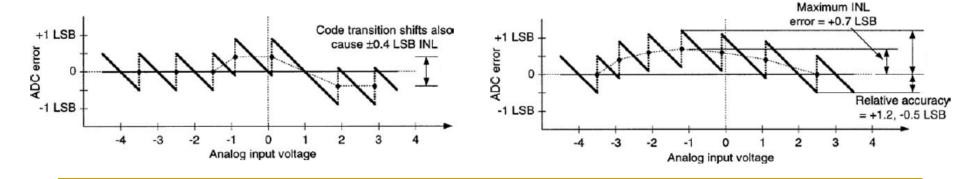

- Integrated nonlinearity error (INL);

- Differential nonlinearity error (DNL);

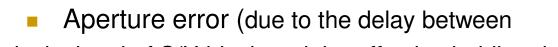

### Dynamic error:

the clock signal of S/H block and the effective holding time)

For sin wave input  $x(t) = A\sin(\omega t)$

$$E_{A} = \left| \frac{\mathrm{d}x(t)}{\mathrm{d}t} \right| T_{A} < \frac{\delta V}{2} \implies T_{A} = \frac{1}{2^{n} \pi f}$$

ADC

Offset error

Gain error

Factor scale error

### Effects of static errors and quantizing error (examples)

An ideal three-bit quantizer, with INL error caused by important DNL error

An ideal three-bit quantizer, with INL error and small DNL error

### Improving A/D conversion techniques

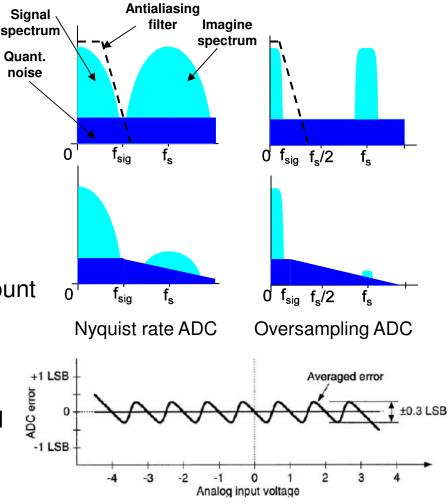

# Oversampling

OSR - oversampling ratio

$$OSR = \frac{f_S}{f_{S\min}} = \frac{f_S}{2 \cdot f_{sig}}$$

$$SNR_q(n) = 6.02 \cdot n + 1.76 + 10 \cdot \log(OSR)$$

**Dithering** — adding a small amount of random noise (maximum =  $1/2 \cdot \delta U$ ) to the input before conversion (for constant and slow varying analog signal).

LSB oscillates randomly between 0 and 1 in the presence of very low input levels.

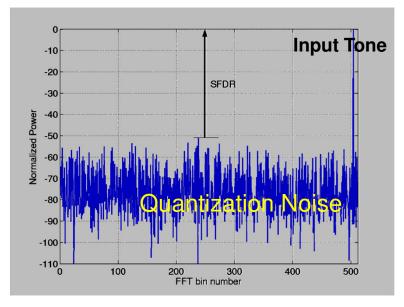

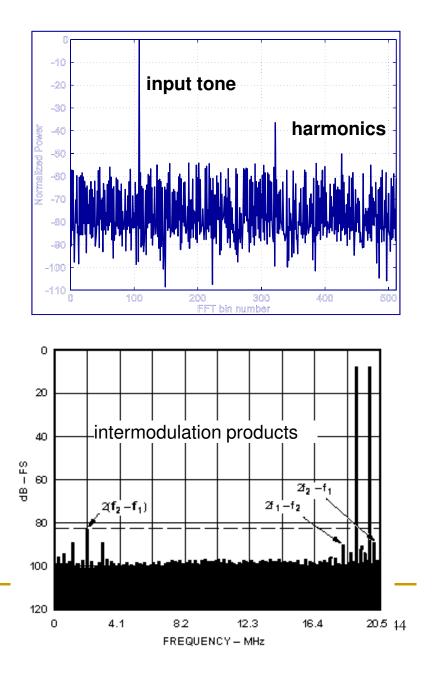

### Acronyms for A/D converter

- SNR Signal to (quantization) Noise Ratio;

- THD Total Harmonic Distortion (due nonzero INL) = the ratio of the rms value of the fundamental sinewave signal to the mean value of the root-sum-square of its harmonics (usually the first five harmonics); Specified in dBc (decibels below *carrier*);

- SINAD (dBc) Signal-to-Noise Plus Distortion ratio (same as SNDR) = ratio of the rms value of the fundamental signal to the mean value of the root-sum-square of its harmonics plus all noise components;

- SNDR Signal to Noise + Distortion Ratio;

- SFDR Spurious Free Dynamic Range = the ratio of the rms value of the signal to the rms value of the worst spurious signal (that may be or may not be an harmonic of the original signal );

Specified in dBc or in dBFS;

$$\square \text{ ENOB - Effective Number of Bits: } n = \left[ \left( SNR \ [dB] - 10,8 \ dB - 20 \cdot \log \left( \frac{U_{x_{eff}}}{U_{ref}} \right) \right) \right] / 6,02 \right]$$

**•** FOM – ADC Figure of Merit :

$$FOM = \frac{Power}{2^{ENOB} f_S}$$

[Joule/level resolved]

Other quantization impairments:

- SFDR

- Harmonics  $m \cdot f_{sin} + n \cdot f_{sample}$ intermodulation products

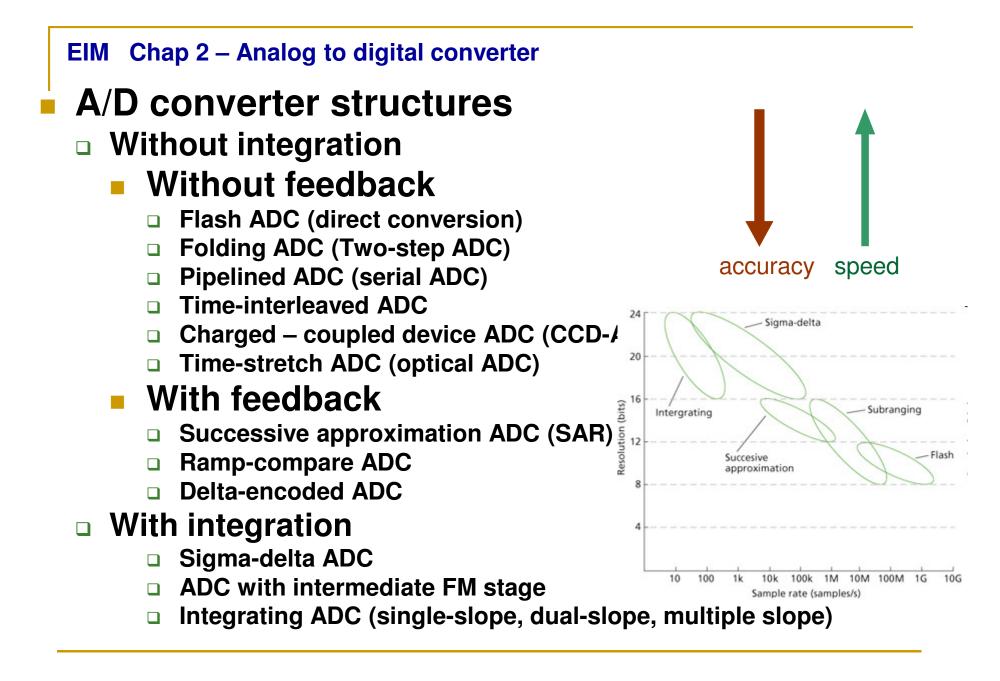

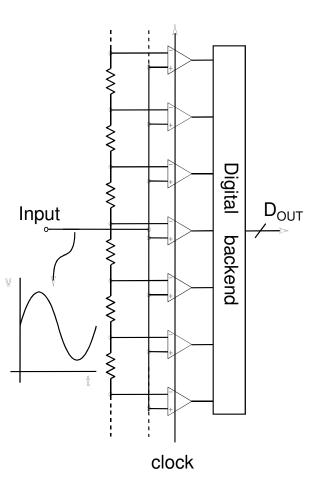

## Flash ADC

• bank of 2<sup>n</sup> -1 parallel comparators (high complexity);

• very fast - GHz sampling rates (limited only by delays of comparators and logic network);

- references resistor ladder

- few bits of resolution (4 8 bits, rarely 10 bits)

- high input capacitance

- expensive power / area (in IC)

- are prone to produce glitches (clock skew comparators sample the inputs at different instants)

- high cost

- applications: video, wideband communications, optical storage

# Flash ADC

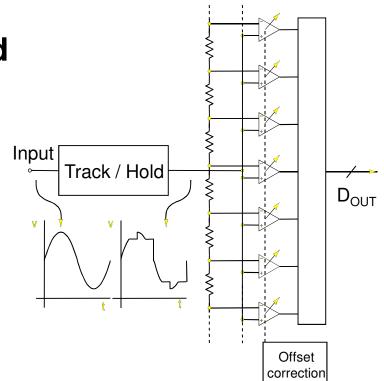

### Improving technique – track / hold

- T/H for good dynamic performance

- Offset correction in comparators

- Example: AD9066 Dual 6-bit, 60MSPS Flash ADC

- Key specifications:

- Input Range: 500mV p-p

- Input Impedance:  $50k\Omega \parallel 10pF$

- ENOB: 5.7 bits @15.5MHz Input

- On-Chip Reference

- Power Supply: Single +5V

- Package: 28-pin SOIC

- Ideal for Quadrature Demodulation

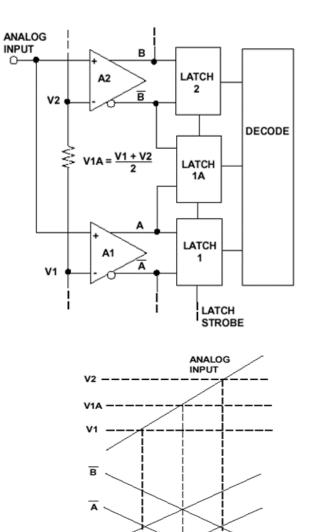

### "Interpolating" Flash ADC

- reduces the number of comparator preamplifiers at the input of a Flash converter by a factor of two;

- substantially reduces the input capacitance, power dissipation, area of flash converters;

- preserves the one-step nature of a Flash architecture (VLSI technology);

в

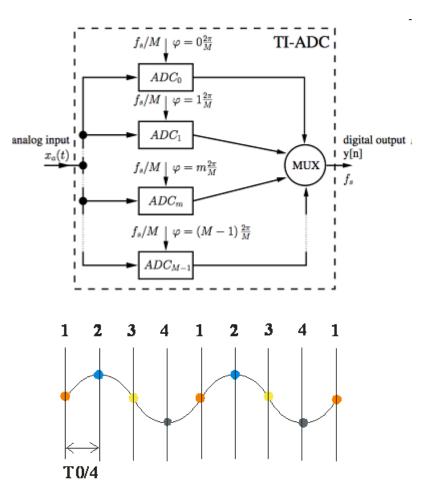

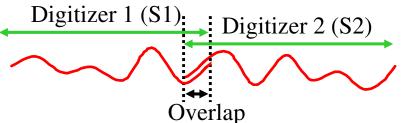

### Time-interleaved ADC (TI-ADC)

- uses M parallel flash ADCs;

- ADC sample data every M-th cycle of the effective sample clock;

- sample rate is increased M times;

- complexity is increased M times;

- requires correction of timeinterleaving mismatch errors;

- applications: video, wideband communications, optical storage;

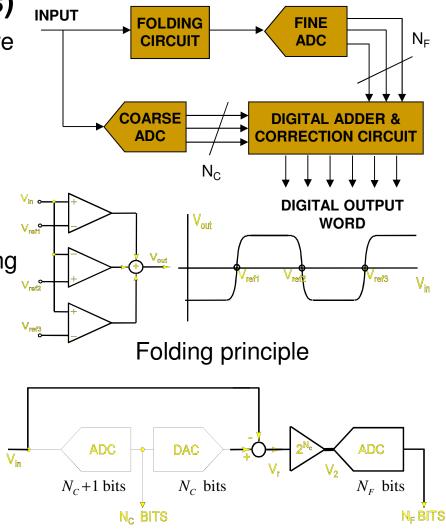

### Folded Flash ADC (two steps)

- Folding = technique that reduces hardware

- maintaining the fast nature of a full Flash ADC;

- An analogue pre-processing circuit generates a residue which is digitised to obtain the LSBs;

- The MSBs are resolved using a coarse ADC that operates in parallel with the folding circuit;

- increase latency;

- Folded ADC reduces latches and logic:  $N_{C}+N_{F}$  bits need  $2^{Nc}+2^{Nf}-2$  comparators;

- First stage determine the output sign;

- At every stage (except the last) the LSB is wasted;

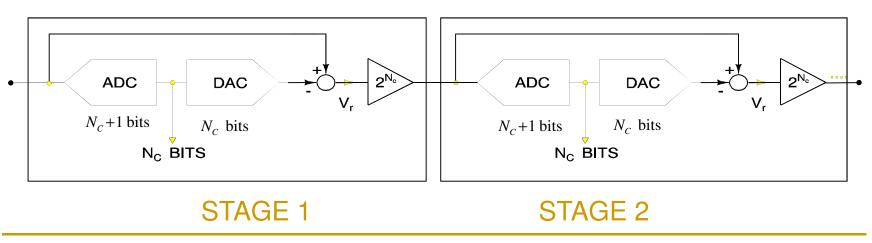

### Serial/Parallel ADC (pipelined)

uses more steps of sub-ranging (with same bits number  $N_C$ );

- one stage

- a coarse conversion is done

- amplifies the difference of the input signal (determined with a DAC), then go to next stage

- fast conversion GHz sampling rates;

- data latency greater than flash, but less than SAR

- high resolution with less complexity;

- ADC overload in next stage need Digital Error Correction;

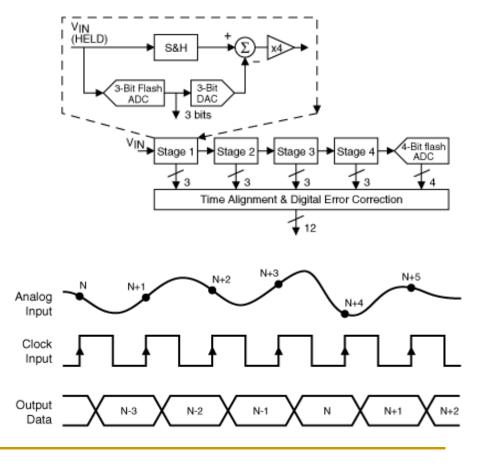

# Serial/Parallel ADC (pipelined)

- Example: AD 9220/9221/9223 12 bits pipelined ADC

- Latency is four cycles;

- 1 bit overlap between adjacent stages

- accuracy of ADC in stages 1-4 needs 4 bits; 5-th stage needs greater accuracy;

- entire ADC accuracy established by 5-th stage

Family Members:

- AD9221 (1.25MSPS), AD9223 (3MSPS), AD9220 (10MSPS)

- Power Dissipation: 60, 100, 250mW, Respectively

- FPBW: 25, 40, 60MHz, Respectively

- Effective Input Noise: 0.1 LSB RMS (Span =5V)

- SINAD: 71 dB

- SFDR: 88dBc

- On-Chip Reference

- Differential Non-Linearity: 0.3 LSB

- Single +5V Supply

- 28-Pin SOIC Package

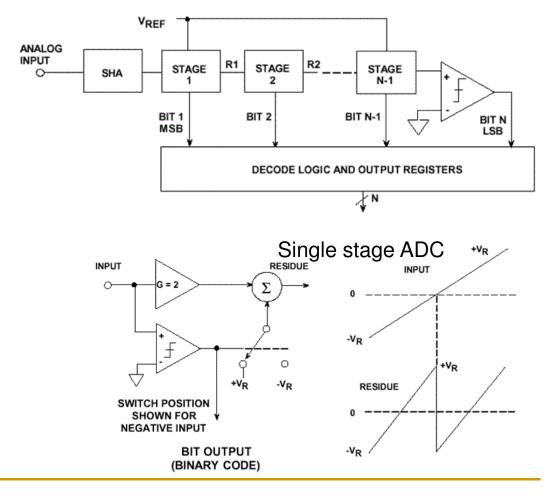

# Serial ADC (1 bit per stage)

- it uses the truncating quantization in intermediate stages.

- Example for bipolar case;

Obs: don't confuse with serial output ADC of other technologies (flash, SAR, folded flash, etc)

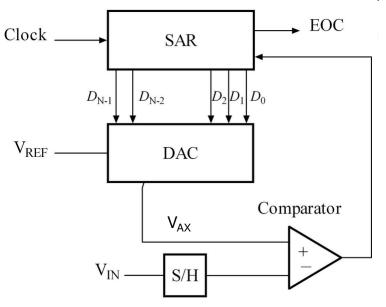

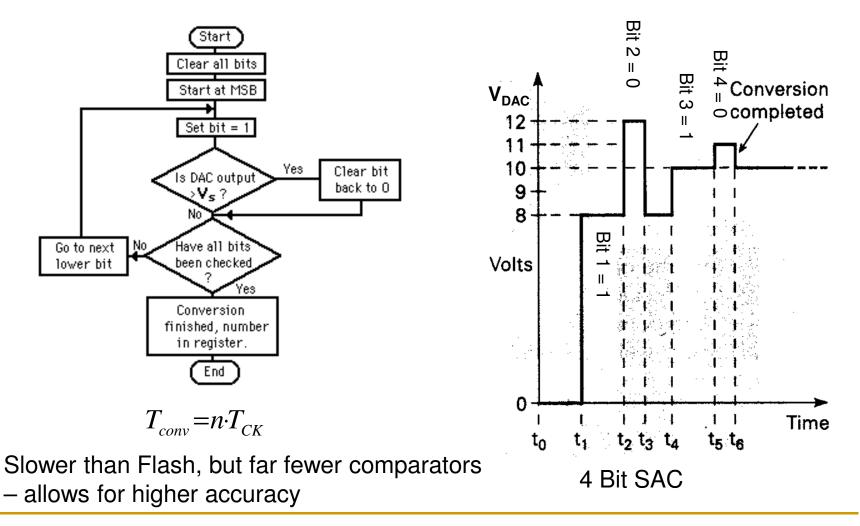

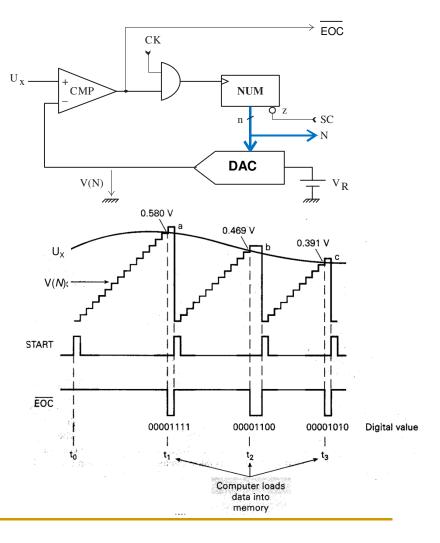

### Successive approximation register ADC (SAR)

- SAR = Successive approximation register

- DAC = digital-to-analog converter

- EOC = end of conversion

- SAR = successive approximation register

- S/H = sample and hold circuit

- Vin = input voltage

- Vref = reference voltage

- use a binary search to converge on the closest quantisation level

- Binary search:

- select middle element

- If too high select middle element of lower group

- If too low select middle element of upper group

- Repeat until 1 element remains

- Constant conversion time (n cycles)

Successive approximation algorithm

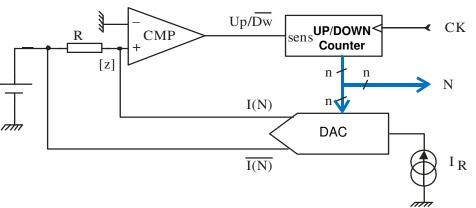

### Delta - encoded ADC (tracking ADC)

- an up-down counter feeds the DAC;

- CMP compares  $U_X$  and DAC output;  $U_x$

- CMP drives U/D counter sens ;

- use a feedback to adjust the counter;

- very wide range and high resolution;

- conversion time is dependent of the input signal level (has a guaranteed value for the worst case);

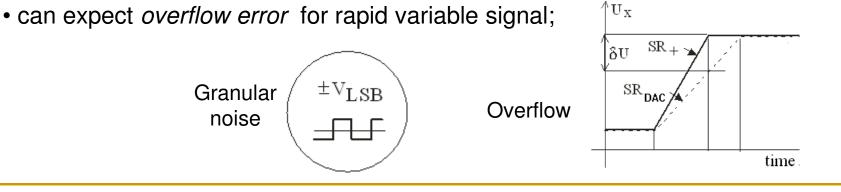

- introduces granular noise for constant and very low frequency signals;

### Ramp Compare ADC

• A comparison voltage V(N) is ramped up;

• When the comparison voltage matches the sampled voltage (VA) the comparator is triggered – the sampled voltage has been determined;

- Variable Conversion Time (depends when ramp signal matches actual signal):

- Best case = 1 cycle

- Worst case = 2<sup>n</sup> cycles

- Slower than SAR, same accuracy;

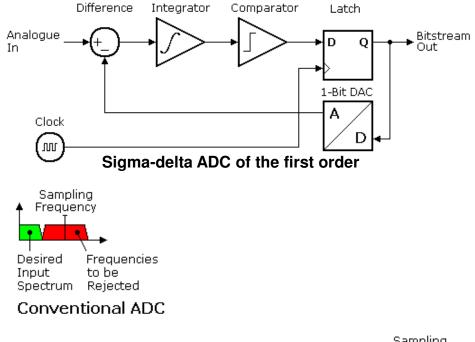

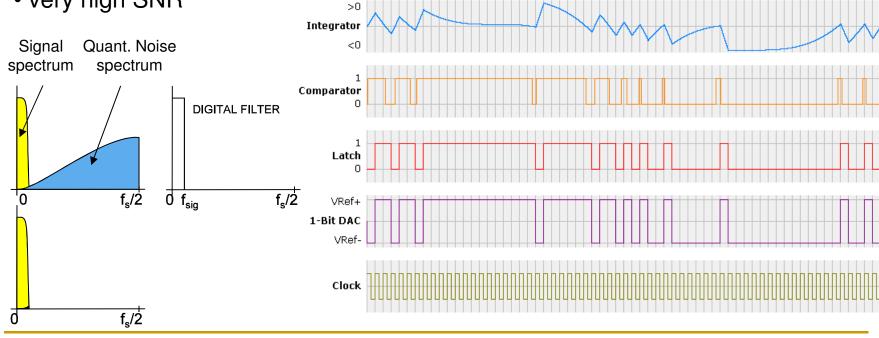

## Sigma-delta ADC

- the output is in the form of a 1 bit serial bit stream;

- analog input variation proportional to the duty of the output digital signal;

- Oversampling (sampling freq 16 512 times greater than Nyquist rate);

- low complexity;

- presents "granular" noise for constants and possible overflow error for fast analog input;

- applications: typical low bandwidth digital transmission 22KHz(voice in digital telephone network); recently - ADSL network access, 1-2MHz (multi-bit ADC and multi-bit feedback DAC ); digital audio equipment (16-24 bit resolution, 48kS/s);

#### Oversampling ADC ( $\Sigma$ - $\Delta$ ADC)

VRef+

Analogue Input

2 x VRef+ Difference

2 x VRef-

VRef-

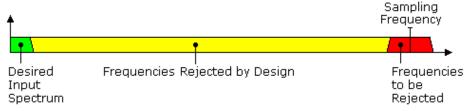

#### Sigma-delta ADC

- Quantization noise is pushed out of the signal band;

- digital filter eliminates out of band noise;

- very high SNR

### Sigma-delta ADC

- better performances for high order

- $\Sigma$ - $\Delta$  ADC (second, third, etc.);

- changing LPF (integrator)  $\rightarrow$  BPF we can

reduce the noise mDSP  $(N_0)$  in band of interest;

VIN

CLOCK

1-BIT DATA STREAM

DIGITAL FILTER

AND

INTEGRATOR

1-BIT

DAC

Second order  $\Sigma$ - $\Delta$  ADC

INTEGRATOR

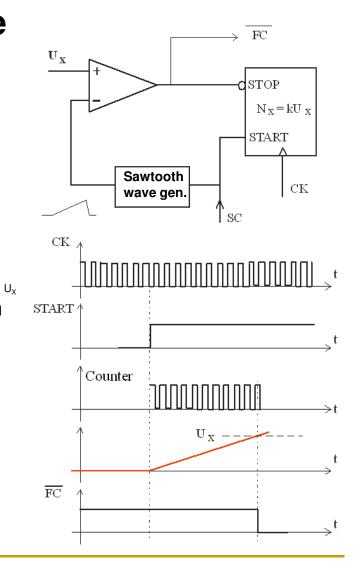

### Integrating ADC – single slope

- similar with ramp compare ADC, but analog ٠ devices

- contain: voltage comparator, digital counter, ٠ sawtooth wave generator

- Phases: ٠

- 0. Reset counter and sawtooth wave generator

- 1. Start conversion (SC) start generator and counter

- 2. Finish conversion (FC) When the comparison voltage (analog input) matches the output generator the conversion finish and stop the counter:

$$N_{X} = k \cdot U_{X}$$

- Variable Conversion Time (depends when ramp ٠ signal matches actual signal):

- Best case = 1 cycle

- Worst case =  $2^n$  cycles

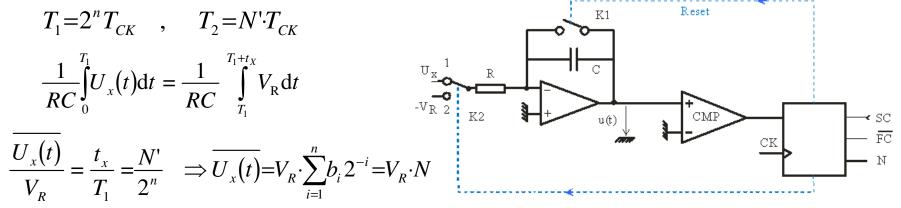

Integrating ADC – dual slope

- Absolute values of R and C don't affect operation

- Conversion time is given by:

$$T_{conv} = (2^{n} + N')T_{CK} \leq 2^{n+1}T_{CK}$$

- Digital output word gives average value of  $U_X$  during first integration phase

- Can be used to get resolutions exceeding 20 bits but at lower conversion rates

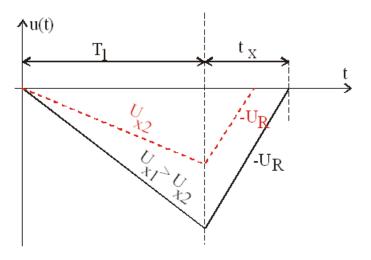

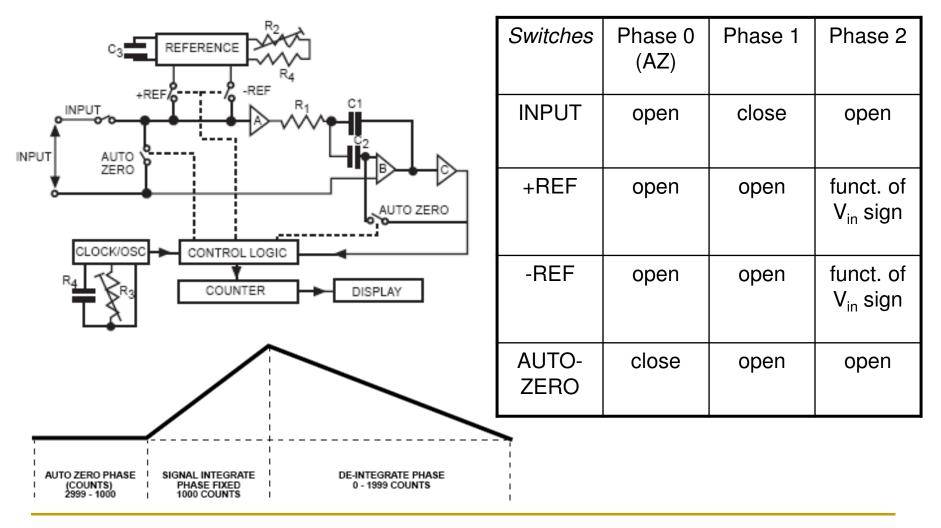

### Integrating ADC – dual slope with auto-zero

• Phase 1 – auto zero ( $K_1=0, K_2=0$ ) •Phase 2 – unknown voltage integrating ( $K_1=1, K_2=1$ )

•Phase 3 - reference voltage integrating (K1=2, K2=2)

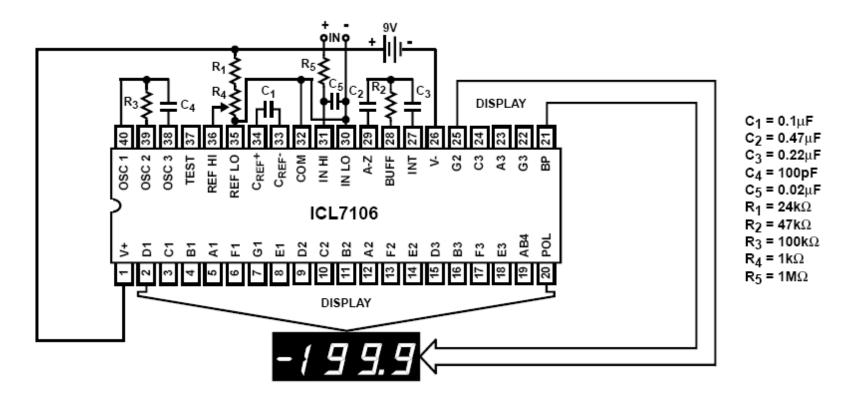

Dual slope ADC application: digital voltmeter

Functioning principle – ICL7106

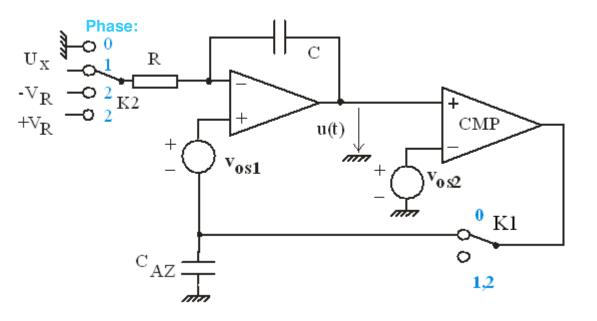

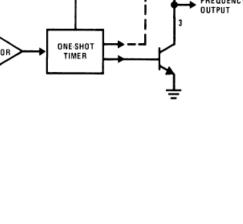

#### <sup>u</sup>GI T1 $\rightarrow t$ -UG R1 U<sub>x</sub>∼fout • a voltage-to-frequency converter AO $U_x > 0$ u<sub>out</sub>(t) CMP • a frequency counter to convert U<sub>CMP</sub> frequency into a digital count u(t) R2 mn -Vp $V_{P} = V_{0} - \frac{1}{R_{1}C} \int_{T_{2}} U_{x}(t) dt$ $\mathbf{GI}$ u(t) 🕆 $V_0 = V_p + \frac{1}{R_2 C} \int_{T_1} U_{GI} dt - \frac{1}{R_1 C} \int_{T_1} U_x(t) dt$ t $V_0$ $\overline{U_x} = \frac{1}{T_1 + T_2} \cdot \frac{R_1}{R_2} \cdot U_{GI} \cdot T_1 = K \cdot f_{out}$ -Vp T2 T1T2T1 $^{\mathrm{u}}\mathrm{GI}$ $^{\mathrm{u}}$ CMP

#### Chap 2 – Analog to digital converter EIM

**ADC** with intermediate FM stage

• comprise

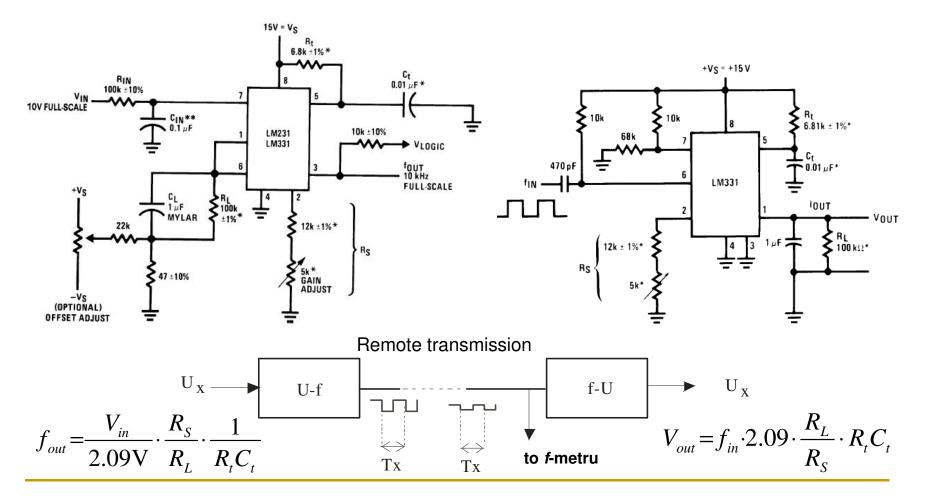

#### **Example U-f converter LM331**

• Longer integration times allow higher resolutions;

• the speed of the converter can be improved by sacrificing resolution;

• few analog devices – high accuracy

are very popular for low frequency application with remote analog sensor;

$$f_{out} = \frac{V_{in}}{2.09 \text{ V}} \cdot \frac{R_s}{R_L} \cdot \frac{1}{R_t C_t}$$

SWITCHED CURRENT SOURCE §<sup>₽</sup>s VLOGIC FREQUENCY OUTPUT INPUT ONE-SHOT COMPARATO TIMER

Ux

# Application. Remote analog voltage measurement with LM331 (National Semiconductor)

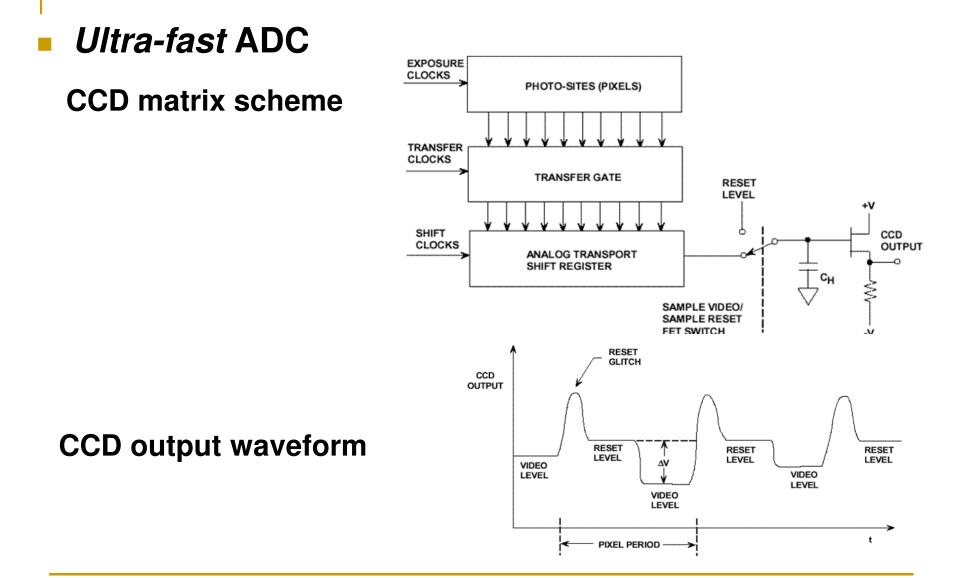

### Ultra-fast ADC

- Pure electronic ADC: CCD-ADC;

- Optical ADC : Time-stretch ADC.

### • CCDs - ADC

Charged-Coupled device (CCD) - sampled analog clocked delay line that memories the input voltage at the clock impulse (analogical memory);

Typically size – 512 stages (samples) and 100MS/s;

An slower ADC quantizes these analogical values;

For greater effective sample rate (400MS/s) are necessary several CCDs

in parallel with staggered clock drive.

Application – digital video signal capturing

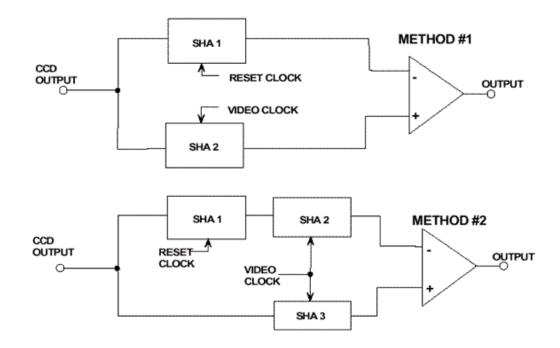

- Ultra-fast ADC electronic ADC

- CCD ADC

Correlated double sampling (CDS) minimise switching noise at output

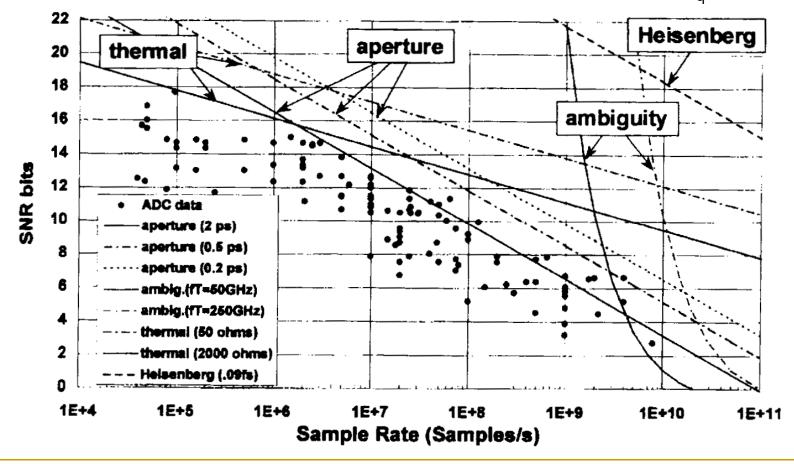

### Ultra-fast ADC – optical ADC

• Electronic (pure) real-time analog-to digital conversion is limited to conversion rates of few GS/s;

• Communication, image processing and radar applications require extremely fast real time A/D conversion;

• A way out of this conversion bottleneck may be the use of photonic concepts for A/D conversion;

Concept for ADC optical conversion:

- Photonic time stretching converter;

- Self-Electro-optic Effect Device based all-optical A/D conversion;

- Optical folding-flash converter;

- Optoelectronic thyristor based photonic smart comparator;

### Ultra-fast ADC – optical ADC (cont'd)

Absolute analog to digital conversion rate limits for a required SNR<sub>a</sub>

### Ultra-fast ADC – optical ADC

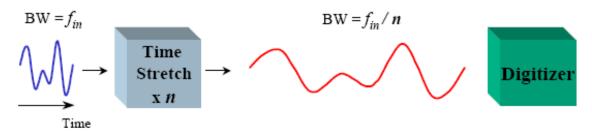

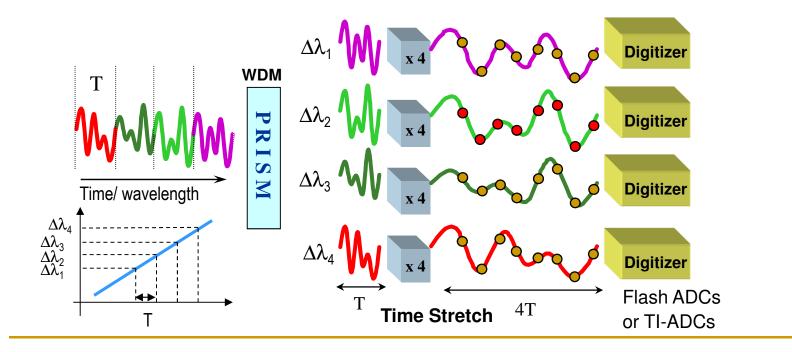

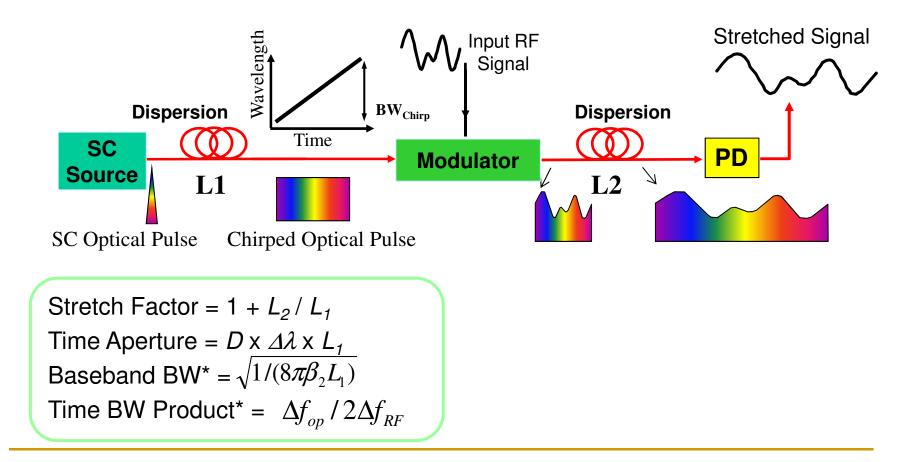

• **Time-stretch ADC (TS-ADC)** Digitizes a very wide bandwidth analog signal by time-stretching the signal prior to digitization using a photonic preprocessor.

- Improvements:

- Effective sampling rate increased by *M*;

- Effective Input bandwidth increased by M;

- Reduce jitter noise ;

- Eliminates the need for samples interleaving ;

- Ideal for time-limited signals or fast time-varying signals ;

### Ultra-fast ADC – optical ADC (cont'd)

### Schematic photonic preprocessor for time-stretching

- Each ADC see the slowed-down signal;

- Full Nyquist sampling by each ADC;

• By allowing for finite overlap between segments, mismatch error can be estimated from the signal itself;

### Ultra-fast ADC – optical ADC (cont'd)

Photonic Time Stretch System

### Ultra-fast ADC – optical ADC (cont'd)

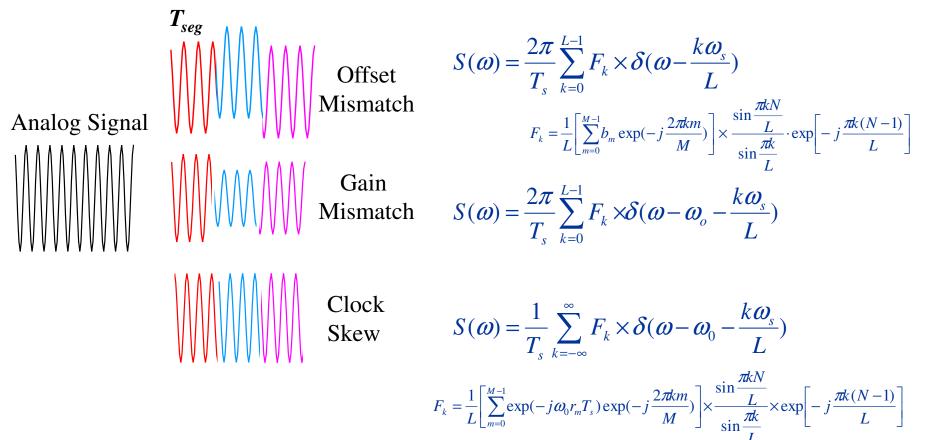

Mismatches in TS-ADC Arrays

L=MxN: the period of distortion pattern

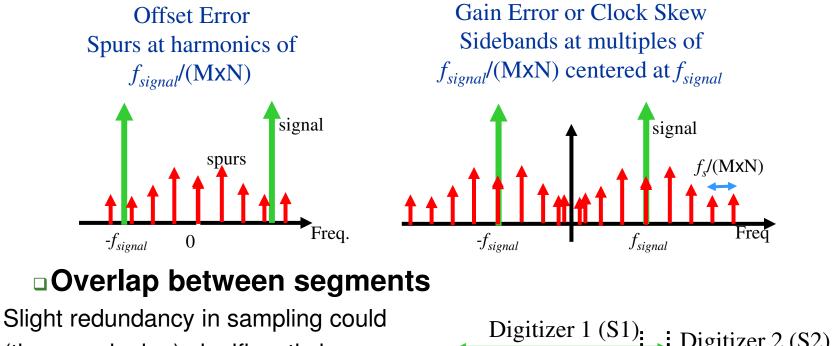

# Ultra-fast ADC – optical ADC (cont'd) Mismatches in TS-ADC Arrays – Spectrum

(time overlaping) significantly improve the ADC performance;

## Ultra-fast ADC – optical ADC (cont'd)

### Time-stretch ADC (TS-ADC)

• ADC SFDR Improvements

|               | RMSE<br>(before) | SFDR<br>(before) | RMSE<br>(after) | SFDR<br>(after) |

|---------------|------------------|------------------|-----------------|-----------------|

| Offset        | 4%               | -36dBc           | 0.3%            | -58dBc          |

| Gain          | 4%               | -36dBc           | 0.35%           | -57dBc          |

| Clock<br>Skew | 8%               | -26dBc           | 0.45%           | -51dBc          |

### Conclusions:

- Signal is reconstructed based on segments, instead of the individual samples;

- In each segment, the sampling is above the Nyquist sampling rate;

- Subject to the similar mismatch as the sample-interleaved counterpart;

# Bibliography

- □ S. Ciochina, *Masurari electrice si electronice*, 1999;

- ham.elcom.pub.ro/iem;

- Application notes National Instruments;

- J.G. Webster, *Electrical Measurement, Signal Processing and Displays*, 2004;